Cool Tips About How To Write Verilog Testbench

All the concepts of hdl coding.

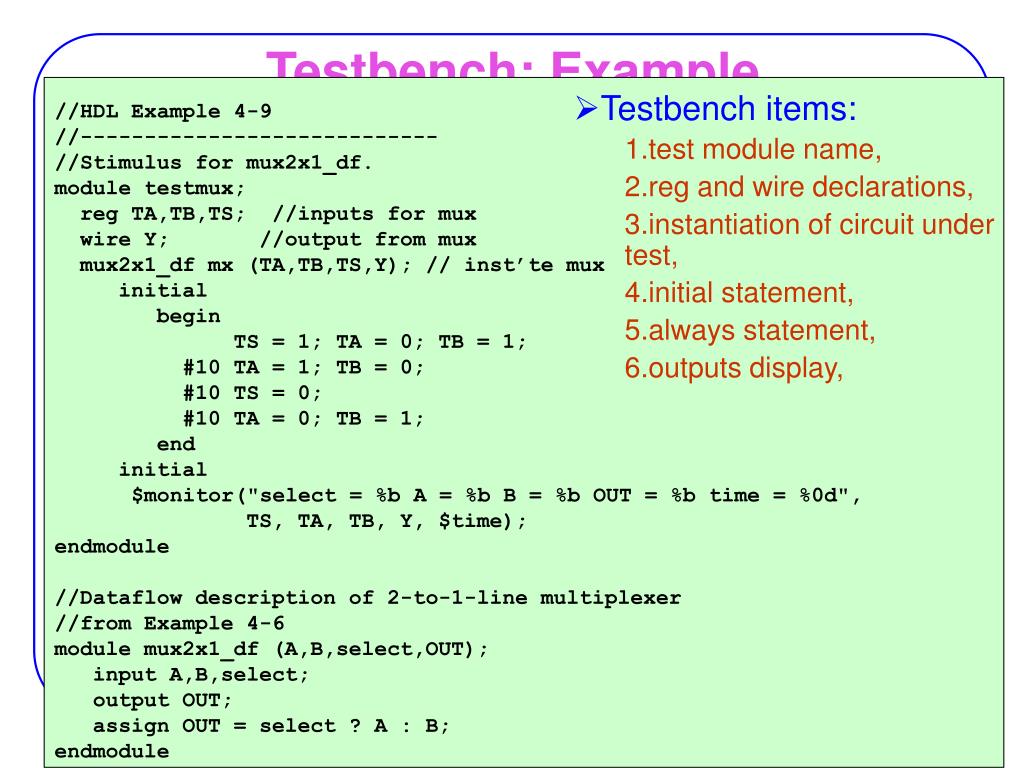

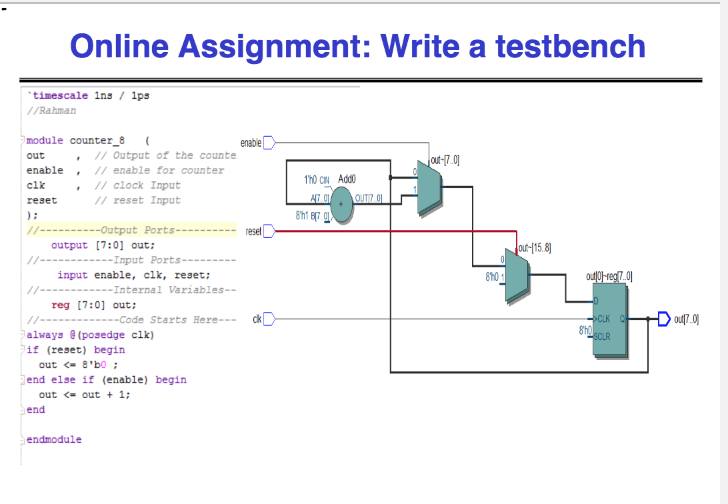

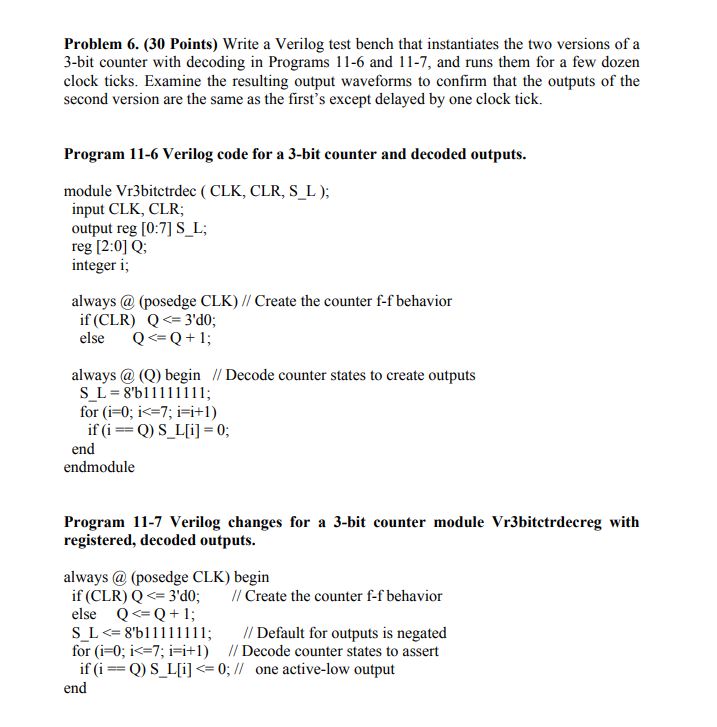

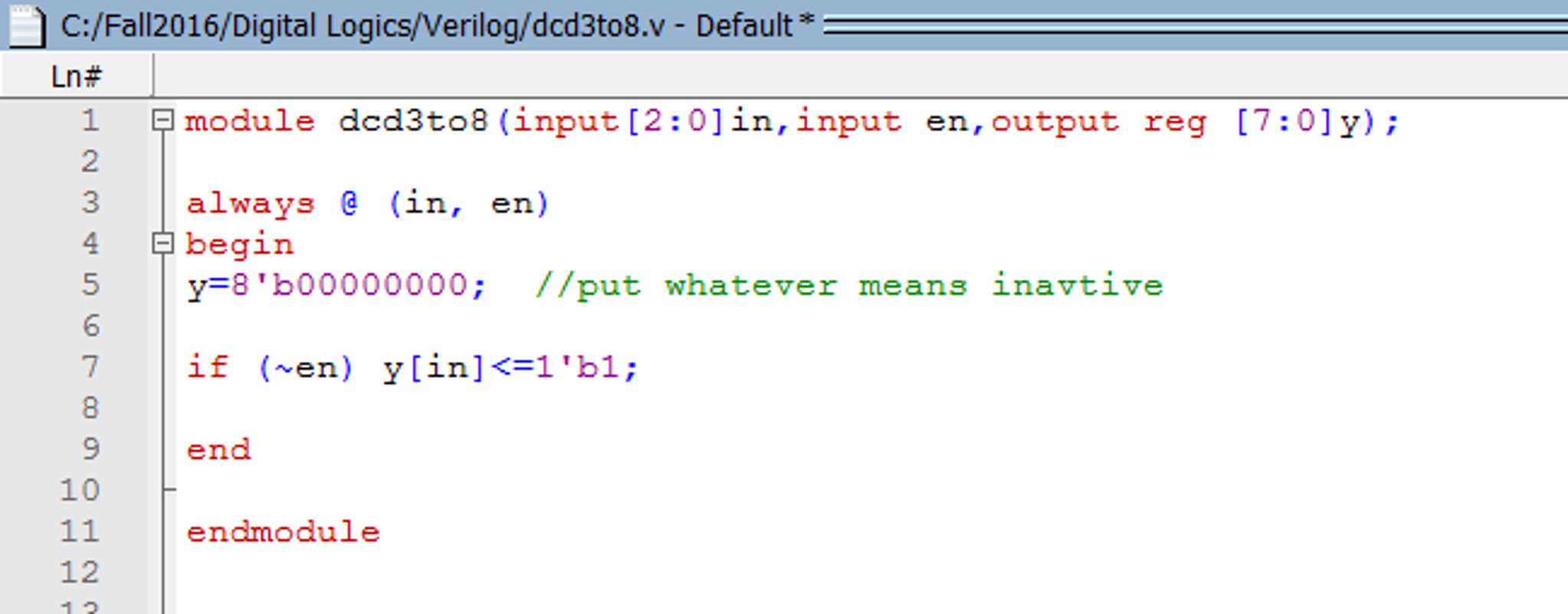

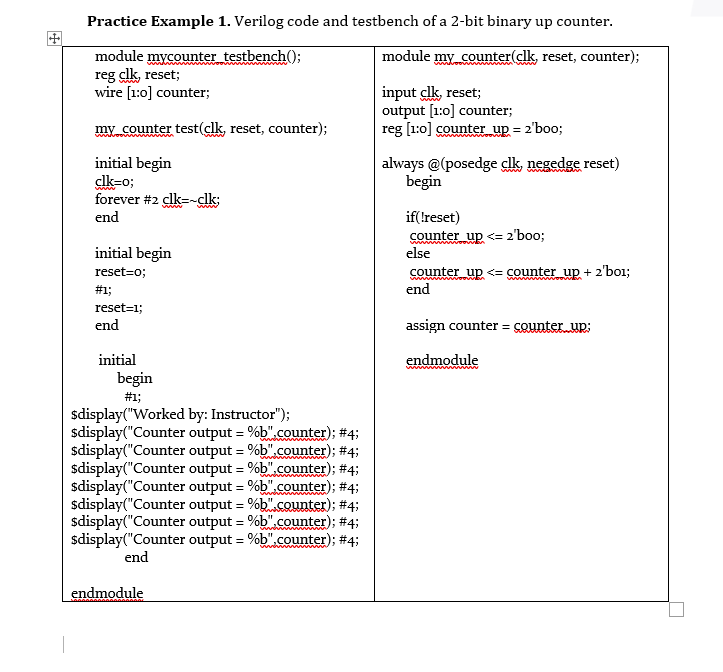

How to write verilog testbench. Using testbench, you can verify the. To write a verilog testbench, we need to create a stimulus block and a response block. Writing testbenches using systemverilog.

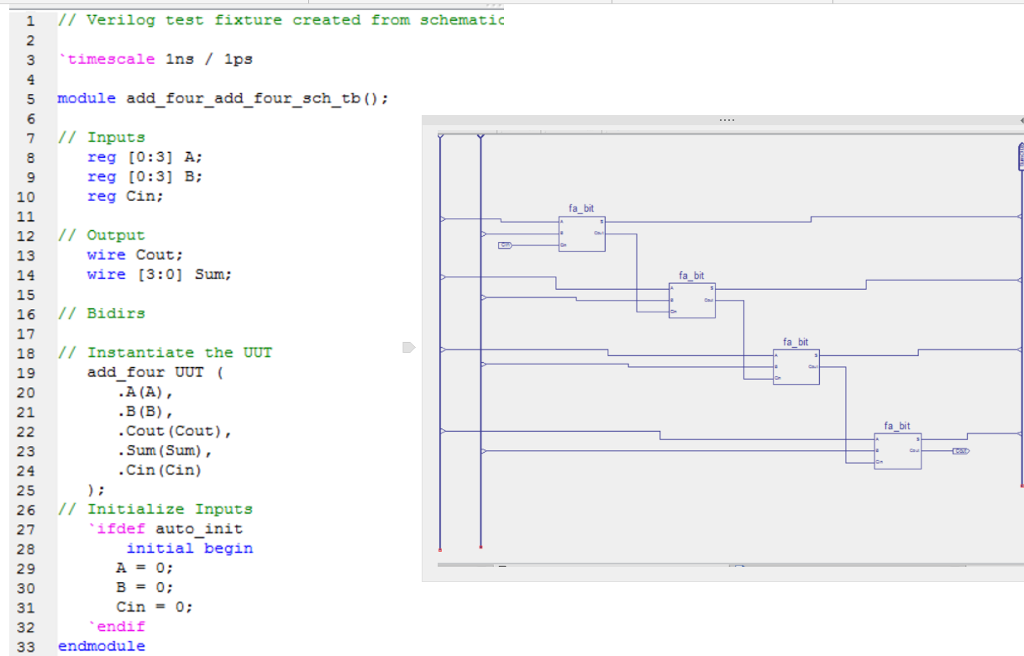

Assuming you're not using systemverilog, you could write a task, eg: Or, you can create new procedural blocks that will be.

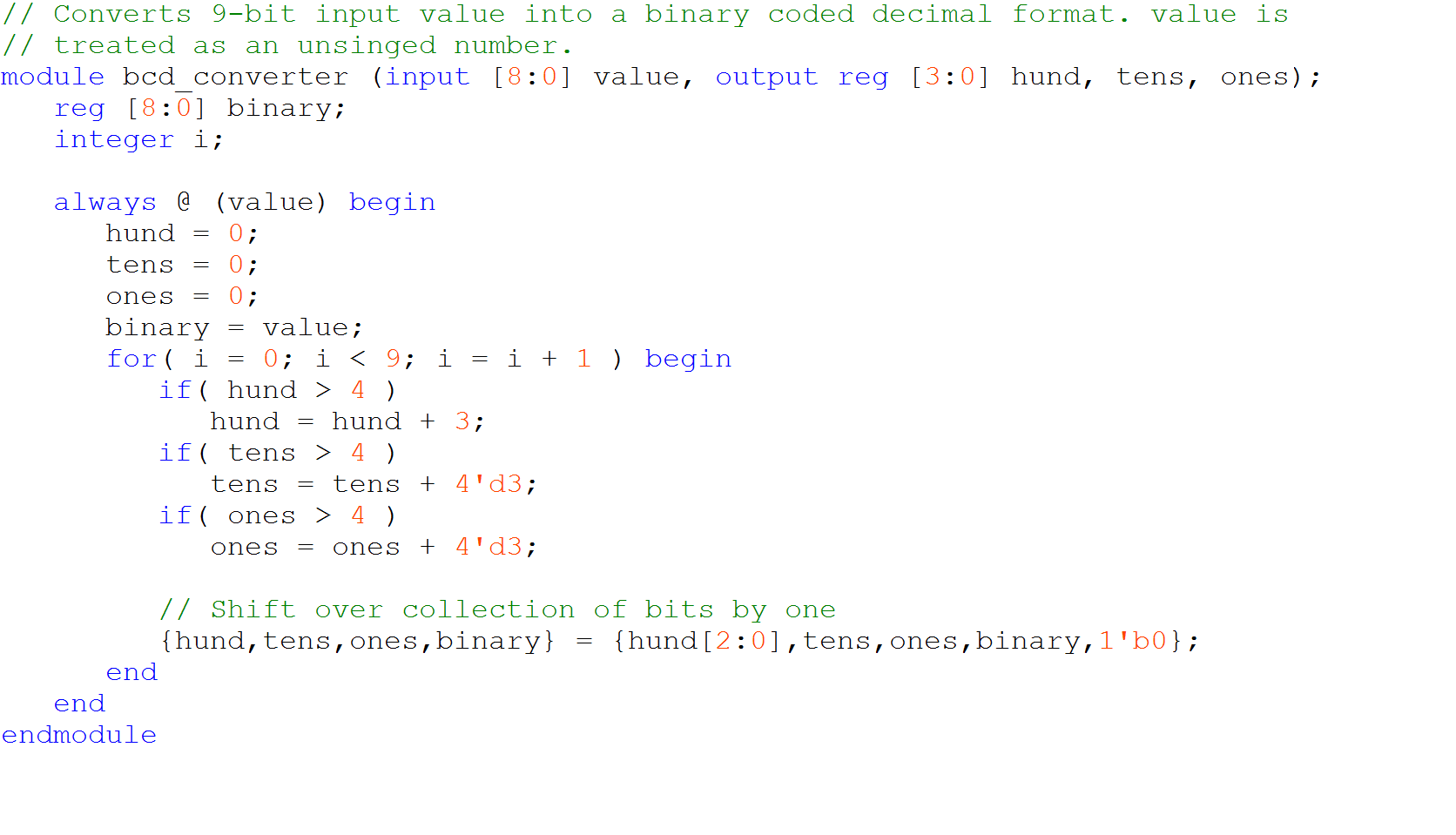

Im having some issues with this code i made. In this post we look at how we use verilog to write a basic testbench. A conventional verilog ® testbench is a code module that describes the stimulus to a logic design and checks whether the.

Video if you have not done so, please watch the following video, which. Testfixture.verilog again, template generated by cadence testbench code all your test code will be inside an initial block! The test bench encompasses the design, it.

The function is to save whatever is on input d to an output q, which can be any of the 32 registers that have been declared. Task lhwrite (input integer bin, input integer length); Simply specify the values of.

Define your modules and inputs. Declare a testbench as a module. What is a verilog testbench?

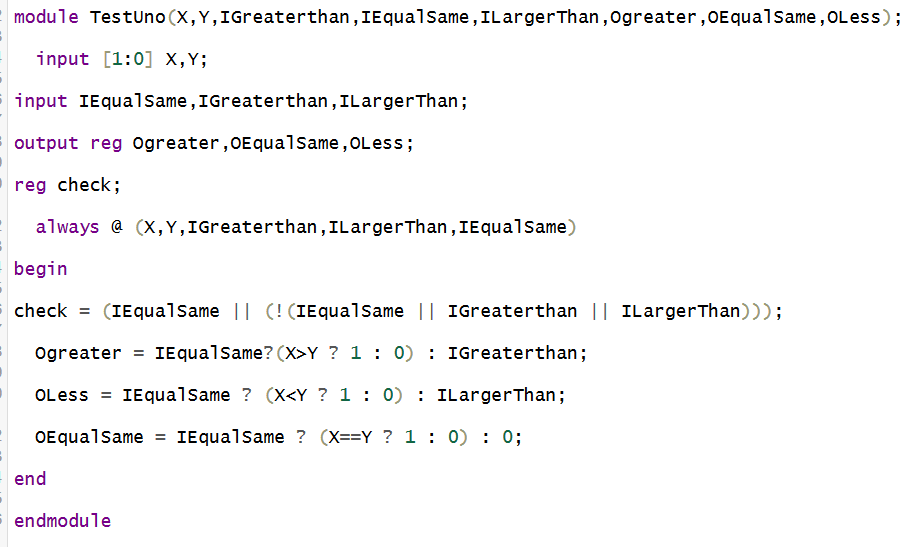

S_tb and v_tb are the expected outputs which are asserted by the design module which in this case is statemachine. How to write testbench in verilog. The testbench is compiled and simulated using a verilog simulator.

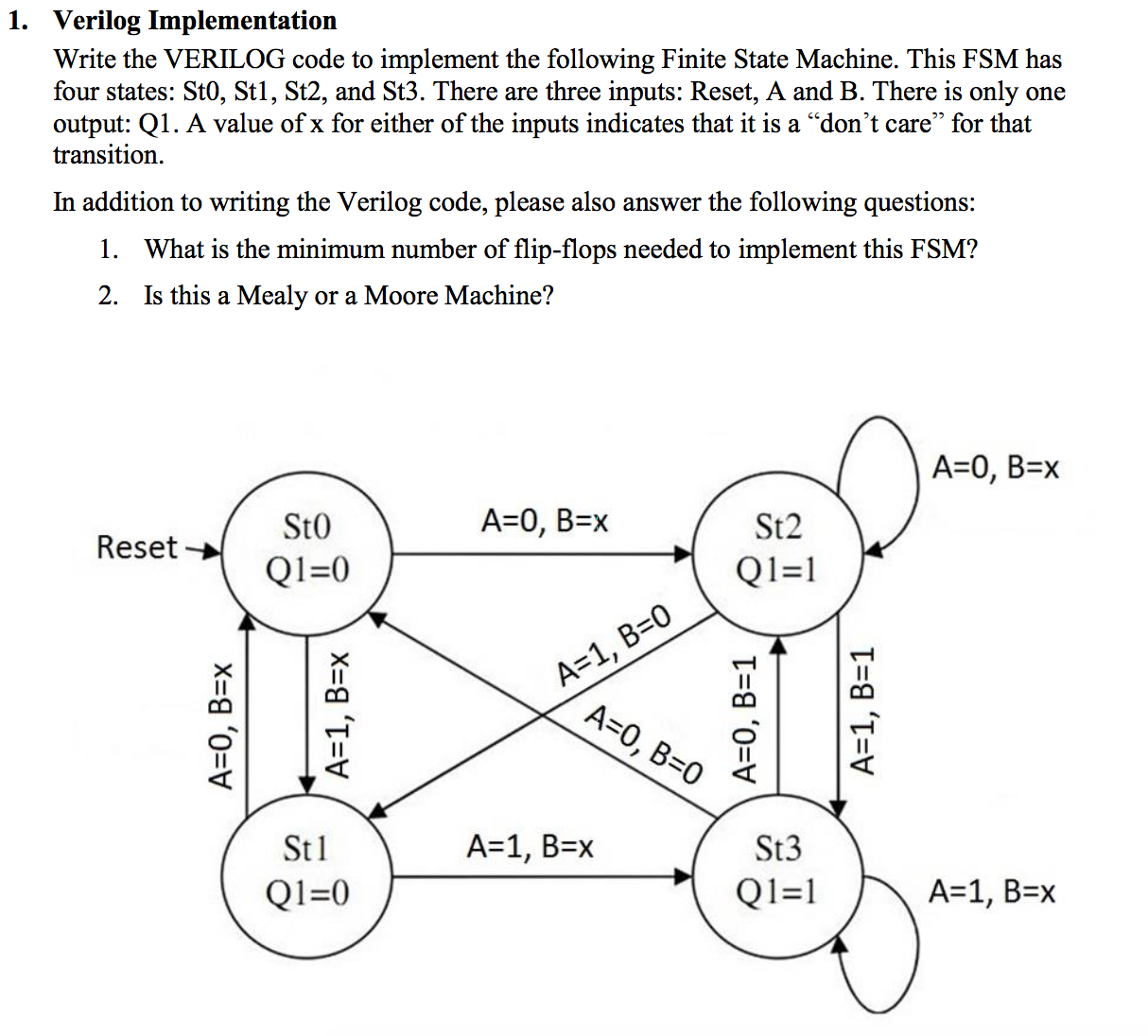

The verilog testbench is written in the same verilog language as the dut. I have to create the verilog code. Basics of verilog hdl programming.

This happens in special designs which contain bidirectional or inout ports such as i2c core,. Click here to refresh basic concepts of a simulation. Steps involved in writing a verilog testbench.

In this guide, we show how to write verilog testbenches and simulate designs using icarus verilog (iverilog). How to write a testbench to loop through 4 inputs? // note that top level testbench module does not need any io ports and.